SPI supports high-refresh OLED displays at rates above 10Mbps.

Although it requires 4-5 pins, its performance is far superior to the I2C protocol, which only needs 2 wires for driving but has a bandwidth of only 400kbps and is prone to stuttering when processing complex dynamic images.

Speed

In standard mode, the I2C clock frequency is only 400kHz or 1MHz, and every 8 bits of data sent requires an additional 1-bit acknowledgment (ACK). This limits the refresh rate for a 128x64 resolution typically to below 20 FPS.

In contrast, SPI frequencies can easily reach 10MHz to 32MHz and utilize stream transmission without acknowledgments.

In the same hardware environment, SPI's pixel throughput is more than 20 times that of I2C, providing display performance exceeding 100 FPS and completely eliminating screen tearing and operation latency.

Frequency Upper Limits Comparison

The standard 100kHz mode requires the rise time to be controlled within 1000 nanoseconds, while the 400kHz fast mode needs to be compressed to within 300 nanoseconds.

If a 10k ohm pull-up resistor is selected, the waveform will show a distinct rounded arc under high-frequency pulses, causing the microcontroller sampling point to fail to accurately identify logic high levels.

Even if the resistance is reduced to 2.2k ohms to speed up the discharge rate, it remains difficult to break through the physical limit of 1MHz.

On the other hand, the SPI interface utilizes a push-pull output circuit, where complementary transistors actively drive the signal line, resulting in extremely sharp edge transitions.

On ordinary FR4 PCB material, even without specialized impedance matching design, SPI can stably maintain clock rates of 20MHz or higher. This creates an order-of-magnitude gap in pixel data movement efficiency at the underlying logic level.

| Protocol Specifications and Physical Parameters | I2C Standard Mode | I2C Fast Mode | I2C Fast Mode+ | SPI Typical Rate | SPI High-Speed Rate |

|---|---|---|---|---|---|

| Clock Frequency (Hz) | 100k | 400k | 1M | 10M | 32M |

| Minimum Pulse Width (ns) | 4700 | 600 | 260 | 50 | 15.6 |

| Rise Time Requirement (ns) | < 1000 | < 300 | < 120 | No strict limit | No strict limit |

| Single Byte Transmission Time (us) | 90.0 | 22.5 | 9.0 | 0.8 | 0.25 |

| Level Driving Method | Passive Pull-up | Passive Pull-up | Passive Pull-up | Active Push-pull | Active Push-pull |

In the technical manuals for SSD1306 or SH1106 controllers, the serial clock cycle in SPI mode can be shortened to a minimum of 100 nanoseconds, corresponding to a 10MHz input frequency.

Although some developers on ESP32 or STM32 platforms use overclocking to run SPI at 20MHz or even 40MHz—with the screen still displaying normally—such operations exceed the official recommended range for electrical stability.

The clock limit in I2C mode is strictly constrained by the chip's internal logic state machine.

Most OLED driver chips require the SCL high-level duration to be no less than 0.6 microseconds in I2C mode.

Combined with the protocol-mandated start bits, stop bits, and the acknowledgment bit (ACK) that must exist after every byte, the bus actually generates a load of 9 clock pulses to transmit 1 byte of valid data.

Calculating the refresh for a 128x64 pixel screen, a single layer of GDDRAM requires writing 1024 bytes. At a 400kHz rate, I2C consumes 23 milliseconds just to send pixel data. If command bytes and address overhead are included, the time to refresh one frame exceeds 30 milliseconds, locking the refresh rate below 30 FPS.

On 8-bit AVR architectures (such as ATmega328P), the hardware I2C controller is governed by specific bit-rate registers and is usually limited to 400kHz.

Even if the prescaler is forcibly modified, signal quality degrades rapidly due to bus drive current limitations.

SPI, however, can directly obtain one-half or one-quarter of the CPU frequency as output through a simple clock divider; achieving a rate of 4MHz or 8MHz requires changing only two lines of register configuration.

On 32-bit high-performance chips like the ESP32, SPI channels possess independent DMA controllers, capable of moving data from memory at 80MHz.

Because SPI does not need to stop and detect the level state of the acknowledgment bit after every byte like I2C, the signal flow is continuous.

This continuity eliminates processor idling generated while waiting for an ACK, allowing SPI to achieve theoretical data frequencies exceeding 500 FPS when handling small-size OLEDs with 32x128 pixels or lower resolutions, providing ample bandwidth reserves for complex graphical UI libraries.

| Hardware Platform Frequency Support | Arduino Uno (16MHz) | ESP32 (240MHz) | Raspberry Pi 4 | STM32F103 (72MHz) |

|---|---|---|---|---|

| I2C Max Measured (kHz) | 400 | 1000 | 1000 | 400 |

| SPI Max Measured (MHz) | 8 | 80 | 125 | 36 |

| I2C Pin Voltage (V) | 5.0 | 3.3 | 3.3 | 3.3 |

| Cable Capacitance Tolerance (pF) | 400 | 200 | 150 | 400 |

When wiring length exceeds 20 cm, 400kHz I2C often experiences communication timeouts or garbled displays. SPI belongs to a low-impedance driving mode and has lower sensitivity to distributed capacitance.

Although long cables can cause signal reflection and electromagnetic interference at frequencies above 10MHz, SPI can maintain a transmission speed of 5MHz over extension lines of 50 cm or more by connecting 22-ohm to 47-ohm matching resistors in series on the clock line.

For applications where the OLED screen needs to be installed far from the main control board, the frequency margin provided by SPI ensures stronger system robustness against external environmental noise.

Handshake Overhead

When communicating with an OLED controller, the microcontroller must first issue a start signal, followed immediately by a 7-bit slave address and a 1-bit read/write selection bit.

These 8 bits are followed by a 1-bit acknowledgment (ACK) sent back by the display. In the logic of driver chips like the SSD1306, every byte must still be paired with a 1-bit ACK even after entering the data transmission phase.

Calculations show that for every 1 byte (8 bits) of pixel information transmitted, 9 clock pulses are actually generated on the physical bus. This 11.1% fixed bandwidth loss cannot be offset by increasing the frequency.

In contrast, the SPI protocol uses a physical Chip Select (CS) pin to determine the communication target. Once the chip select signal is pulled low, every clock pulse flowing on the bus is used to move valid bit information.

SPI does not require address frames or acknowledgment detection stages, allowing the data stream to be completely continuous. This structure enables SPI to save at least 1024 clock cycles of waiting time compared to I2C when processing a 1024-byte full-screen data buffer.

The table below shows the protocol overhead distribution for I2C when transmitting different amounts of data at a 400kHz clock:

| Data Volume (Bytes) | I2C Total Bit Expenditure (incl. ACK/Start/Stop) | SPI Total Bit Expenditure (incl. CS Toggle) | Bandwidth Utilization (I2C) | Bandwidth Utilization (SPI) |

|---|---|---|---|---|

| 1 | 20 bits | 8 bits | 40.0% | 98.2% |

| 16 | 164 bits | 128 bits | 78.0% | 99.5% |

| 128 | 1182 bits | 1024 bits | 86.6% | 99.8% |

| 1024 (Full Screen) | 9230 bits | 8192 bits | 88.7% | 99.9% |

In I2C mode, a control byte must typically be inserted before each data transmission. This byte contains the Co bit and the D/C bit, occupying 9 clock cycles.

If multiple coordinate positioning commands are required in a complex UI interface, these control bytes accumulate rapidly.

SPI handles this switching through an independent physical pin (DC pin).

Changing the pin level on the microcontroller takes only 1 instruction cycle, usually completed within tens of nanoseconds, without consuming any bandwidth on the clock line.

In applications that refresh waveforms or animations in real-time, the I2C microcontroller must constantly stop to detect whether the display has sent back an ACK signal.

- Address Recognition Phase: I2C must produce 8 bits of data plus 1 bit for ACK; this process occurs every time transmission starts.

- Acknowledgment Waiting Cycle: After sending 8 bits of data, the microcontroller must release control of the SDA bus and observe its level state. This mode switching increases the complexity of the internal state machine.

- Start and Stop Signals: I2C start and stop conditions require specific level setup and hold times. In high-speed communication, these microsecond-level pauses accumulate into millisecond-level delays.

- Control Bit Overhead: SSD1306 must include control information before every continuous data stream in I2C mode, preventing the seamless long-byte-stream writing possible with SPI.

- Bus Arbitration Load: Even if there is only one OLED screen on the bus, the I2C hardware logic still performs collision detection, increasing underlying hardware processing time.

In I2C mode, the DMA engine must be interrupted by hardware logic after every byte transferred to judge the acknowledgment state, leading to frequent stalls in the DMA pipeline.

SPI is a typical streaming protocol. Due to the absence of the ACK bit, DMA can push display buffer content from memory to the bus all at once at the maximum clock frequency.

At a 10MHz SPI frequency, sending 1024 bytes of data takes only 0.8 milliseconds, with CPU usage close to 0%.

In I2C mode, even in 1MHz fast mode, the same task would take over 10 milliseconds due to the additional burden of protocol handshaking.

When screen resolution increases to 128x128 or when using color OLEDs (such as SSD1351, where each pixel requires 16 bits of color data), the impact of handshake overhead is amplified exponentially.

On a 128x128 color screen, the data for a full frame reaches 32,768 bytes.

Measured Frame Rate Performance

On a 128x64 pixel SSD1306 monochrome OLED screen, frame rate performance most intuitively reflects the chasm in bus efficiency.

Testing with I2C mode at a 400kHz frequency, transmitting a 1024-byte full-screen buffer requires generating at least 9216 clock pulses at the physical level.

Considering I2C control bytes, start bits, stop bits, and the acknowledgment bits following every byte, the actual bus occupancy time is approximately 24 milliseconds.

If the program includes frequent coordinate positioning instructions, the time per frame climbs to 30 milliseconds. At this point, the theoretical upper limit of the screen's refresh rate is locked at around 33 FPS.

In a real development environment, due to the software overhead of the microcontroller processing the I2C protocol stack, the measured stable refresh rate usually hovers between 18 and 22 FPS.

At this rate, rapidly moving text or scrolling menus will show obvious ghosting, with a visual experience similar to the motion blur of early LCD screens, failing to meet the needs of high-performance interactive interfaces.

| Test Scenario (128x64 Monochrome) | I2C Measured Time (ms) | SPI Measured Time (ms) | I2C Stable Frame Rate (FPS) | SPI Stable Frame Rate (FPS) |

|---|---|---|---|---|

| Plain Text Refresh | 12.5 | 0.5 | 80 | 150+ |

| Full Screen Pixel Fill | 28.2 | 1.1 | 35 | 150+ |

| Complex UI Scroll Animation | 45.0 | 2.5 | 22 | 120 |

| Real-time Waveform Display | 52.0 | 3.2 | 19 | 110 |

When the clock frequency is set at a conservative value of 10MHz, the pure physical time to transmit 1024 bytes is only 0.819 milliseconds.

Even accounting for DC pin mode switching and CS signal synchronization, the entire frame data movement can be completed within 1 millisecond.

Theoretically, SPI can push over 1000 frames per second.

Although the internal hardware refresh frequency of driver chips like the SSD1306 is usually limited to between 100Hz and 150Hz, SPI's extremely short bus occupancy time frees up massive processing space for the CPU.

Under a 10MHz SPI drive, the measured frame rate can easily stabilize at the screen's own hardware limit, which is 100 FPS.

At this speed, UI animation transitions appear extremely smooth, completely eliminating visible tearing, and can even run 60 FPS pixel-style mini-games without any perceived input lag.

Color pixels typically use the RGB565 format, where each pixel requires 16 bits (2 bytes). Refreshing the full screen once requires transmitting 32,768 bytes of content.

In 400kHz I2C fast mode, simply transmitting these pixel bits would consume about 0.74 seconds. Adding protocol headers and control overhead, the refresh time per frame approaches 1 second.

Users operating menus would see the screen overlap slowly like a curtain being drawn, losing all interactive value.

In 10MHz SPI mode, moving 32,768 bytes takes only about 26 milliseconds, allowing the frame rate to still maintain around 38 FPS. If the SPI clock is increased to 20MHz, the frame rate can reach over 70 FPS.

This performance makes SPI the only viable solution for color OLED screens in the embedded field, ensuring system performance does not get stuck at the level of static image display.

| Color Screen Test (128x128 16-bit) | I2C (400kHz) Performance | SPI (10MHz) Performance | SPI (20MHz) Performance |

|---|---|---|---|

| Single Frame Data Volume (Bytes) | 32768 | 32768 | 32768 |

| Theoretical Transmission Time (ms) | 737.3 | 26.2 | 13.1 |

| Measured Max Frame Rate (FPS) | 1.2 | 35.5 | 68.2 |

| Visual Smoothness Description | Severe slideshow feel | Relatively smooth | Very silky smooth |

In I2C mode, because the bus rate is low and there is acknowledgment waiting, the microcontroller's I2C peripheral occupies system resources for long periods, causing jitter in real-time tasks.

Measurements show that when an ESP32 runs a Bluetooth protocol stack in the background while driving an OLED via I2C, the screen refresh rate drops from 20 FPS to 12 FPS due to bus conflicts and waiting for acknowledgment signals, resulting in obvious visual stuttering.

Because the SPI interface transmits data extremely quickly, each refresh occupies the bus for a very short time. Combined with DMA technology, the CPU can hand over display tasks to the hardware peripheral within tens of microseconds.

In this multitasking environment, the SPI-driven screen can still maintain a stable 60 FPS without being disturbed by increased system load.

DMA combined with SPI can significantly reduce the time squeezed from the main program logic by display updates.

Testing found that using the U8g2 library in full-page mode to refresh a 128x64 screen takes about 32 milliseconds in I2C mode.

Because the library needs to process complex font rendering and geometric algorithms, choosing I2C results in rendering plus transmission time reducing the total frame rate to around 15 FPS.

Using the same hardware and algorithm logic but switching to the SPI interface, the transmission time is reduced to an almost negligible level, and the total frame rate immediately recovers to over 45 FPS.

Hardware Load Differences

At a clock rate of 400kHz, transmitting one byte physically consumes about 22.5 microseconds.

If the underlying code is written in a blocking manner, the microcontroller's CPU can perform almost no other computational tasks during these 22.5 microseconds.

For an 8-bit processor with a main frequency of 16MHz, this equates to a loss of approximately 360 instruction cycles.

When processing a full-screen refresh at 128x64 resolution, the 1024-byte data volume causes the CPU to fall into a cumulative wait state of over 23 milliseconds.

Even when using a non-blocking interrupt method, frequently triggered byte-completion interrupts cause the CPU pointer to constantly jump between the main program and interrupt service routines.

- Register Configuration Complexity: The I2C module needs to configure prescalers, address registers, and complex control registers to handle start and stop conditions; SPI, by comparison, only requires setting the division ratio and polarity.

- Bus Occupancy Duration: SPI transmits the same amount of data in 0.8 microseconds at 10MHz, allowing the CPU to complete peripheral handover in a very short time and reducing the probability of tasks being suspended.

- State Machine Response: I2C hardware must monitor level conflicts and slave acknowledgment signals on the bus in real-time. Any level error caused by electrical interference triggers complex error recovery mechanisms.

- Handshake Logic Overhead: Due to the hard requirement of the ACK bit, the hardware must pause for one clock cycle after every 8 bits to read the SDA line state. This tiny pause accumulates into significant performance loss in long data streams.

- Pin Driving Method: I2C's open-drain output results in slow rising edges. When processing this asymmetrical waveform, the microcontroller's output driver is less efficient internally compared to the push-pull output of SPI.

The SPI interface is naturally a streaming structure. The DMA engine can push the display buffer from memory to the SPI shift register in a seamless manner, during which no CPU logic intervention is required.

When sending 1KB of OLED data, the CPU only needs to write to the control register once at the beginning, and can then process wireless communication or sensor fusion algorithms.

SPI DMA transmission is done in one breath, and its occupancy of the internal bus matrix is extremely regular.

In contrast, I2C in DMA mode is still limited by the protocol framework. Many hardware implementations still require CPU intervention for state transitions when sending address frames or handling NACK errors.

This makes I2C DMA solutions frequently experience bus arbitration requests in practice, increasing the access latency of the main memory.

- Bus Bandwidth Utilization: SPI can almost fully utilize the theoretical bandwidth of the peripheral bus, while about 11% of I2C's physical bandwidth is occupied by ACK bits, directly increasing the total duration of DMA movement.

- Interrupt Trigger Frequency: SPI usually only needs to trigger a DMA interrupt once after a whole block of data is sent, whereas some I2C implementations might require segmented triggers to handle address retransmission.

- Memory Consumption Difference: To match the I2C control protocol, it is sometimes necessary to build non-contiguous buffers in memory containing control bytes, which is more wasteful of RAM than SPI's method of pointing directly to the raw pixel array.

- Clock Source Dependency: I2C requires high precision for clock frequency. At high frequencies, the microcontroller must use a more stable clock source, which might prevent the phase-locked loop from being turned off in low-power modes.

From an electrical characteristic standpoint, the pressure I2C puts on the microcontroller's I/O modules should not be ignored.

Because it uses external pull-up resistors, the microcontroller pins must continuously sink current when at a logic low level.

When refreshing an OLED at high speed, the SDA and SCL pins frequently switch between high and low levels. This continuous current inflow increases local heating within the chip.

In comparison, SPI uses push-pull driving, where current is generated only in spikes during level transitions, and static power consumption in a steady state is extremely low.

For battery-powered portable devices, if the OLED screen requires real-time image updates, using the I2C protocol will lead to higher overall power consumption for the microcontroller because the duty cycle of the peripheral controller and pin drivers is much higher than in SPI mode.

- Heat Distribution: When working at high frequencies, the power density of the I2C controller and its related pin drivers on the silicon die is higher than that of the simpler SPI shift register.

- Signal Integrity Compensation: When handling I2C's capacitive load, the CPU may need to adjust pin drive strength or enable slope control functions. These additional hardware feature configurations increase the amount of initialization code.

- Electromagnetic Compatibility (EMC) Handling: SPI push-pull signal edges are too sharp, sometimes requiring drive capability to be lowered in software to reduce EMI. While I2C rising edges are slower, the wide-spectrum noise they generate is harder to evade through simple configuration.

I2C communication is often classified as a time-consuming operation due to its low bus rate and acknowledgment waiting.

If the screen refresh task is placed in a high-priority thread, it will monopolize the bus for a long time, preventing other lower-priority tasks from gaining timely access to peripherals.

If I2C operations are placed in a low-priority task to balance performance, because the transmission time is as long as tens of milliseconds, display content is likely to suffer from obvious refresh delays or screen tearing due to being frequently interrupted by high-priority interrupts.

SPI, with its sub-millisecond full-screen movement capability, allows display tasks to be completed as quickly as a regular memory copy.

This greatly simplifies task scheduling logic in real-time systems, allowing the CPU to allocate balance more evenly between computational tasks and peripheral management.

Pin Count

The I2C protocol physical link requires only SDA and SCL signal lines, totaling 4 pins including power, occupying 2 GPIOs on the controller.

The SPI protocol in 4-wire mode requires MOSI, SCK, CS, and DC signal lines, and usually also requires 1 RESET line, totaling 6 to 7 pins.

In Arduino or ESP32 development, the SPI solution consumes 150% more IO resources than I2C.

I2C supports multiple devices sharing the bus without adding pins, whereas SPI must add 1 CS pin for every additional screen connected.

Interface Connection Standards

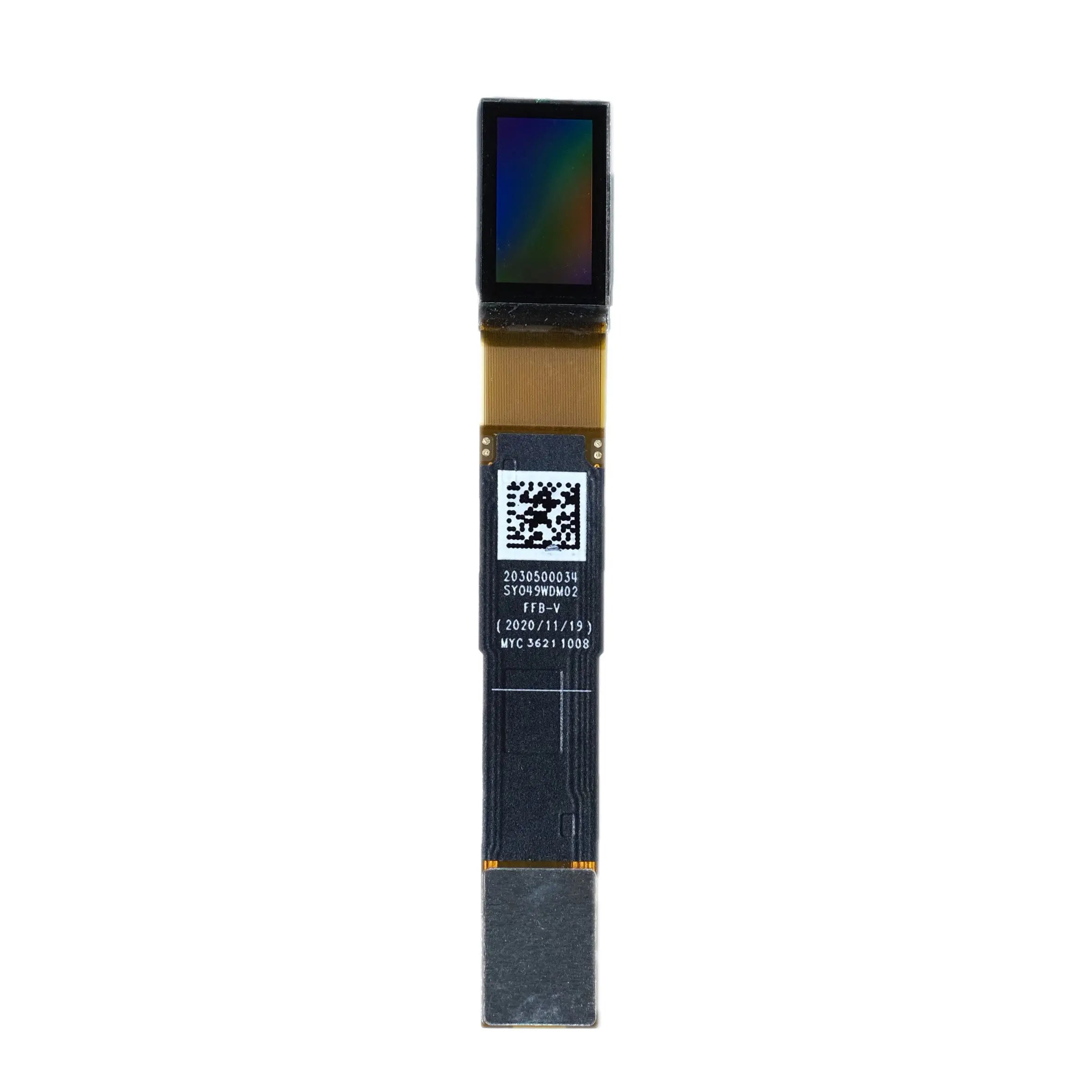

Common 128x64 pixel OLED modules mainly follow two types of physical connection standards at the hardware level: a 2.54mm pitch header interface designed for direct microcontroller insertion, and an FPC (flexible printed circuit) interface designed for ultra-thin devices.

For screens using SSD1306 or SH1106 driver chips, I2C versions of the module usually only lead out four solder pads: VCC, GND, SCL, SDA.

SPI versions lead out 6 to 7 pads depending on protocol completeness, including D0 (Clock), D1 (Data), RES (Reset), DC (Data/Command Select), and CS (Chip Select).

On a 0.96-inch PCB, the space occupied by an I2C interface layout is typically around 10 mm by 3 mm, while the SPI interface's horizontal span increases to over 18 mm due to the three additional signal lines.

For PCB layouts of space-constrained small wearable devices, this physical size difference manifests as squeezed routing channels.

| Pin Function Description | I2C Standard Definition | 4-Wire SPI Standard Definition | 3-Wire SPI Standard Definition | Electrical Parameters/Level Requirements |

|---|---|---|---|---|

| Positive Power | VCC (2.8V-5.5V) | VCC (2.8V-5.5V) | VCC (2.8V-5.5V) | Static current ~10uA, full brightness ~20mA |

| Power Ground | GND | GND | GND | Must share common ground with controller |

| Serial Clock Line | SCL | D0 (SCK) | D0 (SCK) | I2C max 400kHz / SPI max 10MHz |

| Serial Data Line | SDA | D1 (MOSI) | D1 (MOSI) | Unidirectional (Controller to OLED) |

| Reset Signal | Internal pull-up/None | RES (Reset) | RES (Reset) | Active low, duration must be >3us |

| Command/Data Toggle | Protocol address control | DC (A0) | 9-bit protocol control | High for Data, Low for Command |

| Chip Select Line | None (Address based) | CS (Chip Select) | CS (Chip Select) | Active low, required for multiple SPI devices |

Standard module onboard resistors are typically between 2.2k ohms and 10k ohms.

If bus capacitance exceeds 400pF, I2C signal integrity drops significantly, leading to communication failure.

Therefore, for long-distance connections, the I2C solution is less stable than SPI.

For physical setting of the device address, standard interfaces usually reserve a configuration bit named SA0 or ADDR.

By connecting this pin to ground or high level, the 7-bit I2C address can be switched between 0x3C and 0x3D.

SPI connection standards are physically more complex. The 4-wire SPI mode adds a dedicated DC (Data/Command) pin to distinguish between drawing data and control instructions at the hardware level.

When sending 128x64 pixel buffer data, the DC pin is held high, allowing the controller to push 1024 bytes of pixel information without interruption; when screen brightness or scroll direction needs to be changed, the DC pin is pulled low.

This hardware switching method avoids the overhead of sending slave address confirmations for every byte in the I2C protocol.

For the 3-wire SPI standard, the DC pin function is integrated into the serial protocol, meaning 9 bits are sent instead of 8, with the 1st bit acting as the DC flag.

Although 3-wire SPI saves one pin, most controllers' hardware SPI controllers do not natively support 9-bit mode, often requiring software simulation (Bit-Banging), which consumes significant processor cycles.

For FPC interfaces of bare screen modules, the connection standard typically uses a 30-pin 0.5mm pitch socket.

In such high-density connectors, pins 1 to 3 are usually defined as NC (not connected), pins 4 to 6 as VSS (ground), and pins 7 to 28 cover internal charge pump capacitor pins (C1P, C1N, C2P, C2N) and VCOMH adjustment pins.

When integrating such bare screens into a custom PCB, focus must be placed not only on SPI or I2C signal lines but also on the configuration of peripheral boost circuit connections.

For example, although SSD1306 VCC input supports 3.3V, its internal OLED panel drive voltage (VPP) usually requires 7V to 9V.

If internal charge pump mode is selected, a non-polar capacitor of 0.1uF to 1uF must be bridged between C1P/C1N and C2P/C2N respectively.

Regarding logic level matching, although most OLED module interfaces are labeled as supporting 5V (due to an onboard LDO regulator), their signal pins (SCL, SDA, MOSI, etc.) are often not 5V tolerant.

When connected to 5V logic microcontrollers, the 3.3V OLED interface might suffer from overheating of the driver chip's internal protection diodes due to high-level backflow.

An ideal connection solution is to add a level shifter circuit on the signal lines or use 4.7k ohm series current-limiting resistors.

Furthermore, the CS chip select pin in the SPI standard acts as physical isolation.

When CS is high, the OLED's D0 and D1 pins enter a high-impedance state, allowing the bus to be occupied by other high-speed peripherals (like SD cards).

I2C Minimal Wiring

Common 0.96-inch SSD1306 driver screen modules usually provide only four metal pads: VCC, GND, SCL, and SDA.

Compared to old 1602 LCD screens that easily require 14 to 16 pins for parallel connection, the I2C solution compresses all data transmission and control logic into just two signal lines.

This design not only reduces physical port occupancy on the microcontroller but also significantly lowers PCB routing complexity.

In extremely space-constrained wearable devices or micro sensor nodes, display functionality can be integrated by leading out only two 0.2 mm wide traces from the controller's hardware I2C port.

For developers using ATmega328P or ESP32, GPIO resources originally intended for other sensors or actuators are liberated.

In physical layout, 4-pin interface modules are usually kept around 27 mm wide, with pin spacing following the standard 2.54 mm (0.1 inch) specification.

-

Physical Connection Pin Definitions:

- VCC Pin: Accepts 3.3V to 5V DC input. An onboard LDO regulator drops the voltage to the level required by the driver chip.

- GND Pin: The system's reference ground; must be at the same potential as the controller's ground to prevent signal floating.

- SCL (Serial Clock): Synchronous clock pulses generated by the master device, determining the transmission pace.

- SDA (Serial Data): Bidirectional data line used for sending initialization commands and pixel dot matrix buffers.

Because the protocol uses a 7-bit addressing mechanism, multiple devices can physically hang on the exact same SCL and SDA traces.

For OLED screens, driver chips usually provide an address configuration pin (typically labeled ADDR or SA0).

By connecting this pin high or to ground, the screen's I2C address can be switched between 0x3C and 0x3D.

Under this wiring method, driving two screens still only requires two signal lines, whereas the SPI protocol requires an additional CS pin for every extra screen.

At the electrical level, I2C's simplicity is supported by an open-drain architecture, which requires pull-up resistors on both the SCL and SDA signal lines.

Most off-the-shelf OLED modules have these resistors pre-installed on the back of the board, with values typically at 4.7k ohms, 5.1k ohms, or 10k ohms. These resistors ensure the bus stays high when idle.

In longer-distance connections (e.g., over 50 cm), distributed capacitance of the wires can cause signal rising edges to become rounded, leading to data verification failure at high frequencies.

In such cases, the simplified wiring cannot hide the challenge of signal integrity, and developers may need to reduce pull-up resistance to 2.2k ohms to speed up level transitions.

Additionally, since I2C only needs two signal wires, physical shielding is more convenient, requiring only a pair of twisted wires or a simple shielding layer to resist electromagnetic interference.

| Parameter Item | I2C Minimal Mode Value/Characteristic | Hardware Impact Details |

|---|---|---|

| Number of Signal Lines | 2 (excluding power) | Consumes very few GPIOs, suitable for 8-pin MCUs |

| Typical Pull-up Resistance | 4.7k ohm | Determines signal waveform rise time |

| Logic Level Compatibility | 3.3V Standard (some support 5V) | Must note controller IO port voltage tolerance |

| Max Routing Length | Suggested < 30 cm | Exceeding this requires lowering frequency or adding drivers |

| Device Addressing Limit | Usually 2 addresses for same model | Switching between 0x3C and 0x3D |

| Bus Capacitance Limit | 400pF Maximum | Longer cables increase capacitance, impacting max frequency |

On an Arduino Nano, SDA corresponds to A4 and SCL to A5; on an ESP32, GPIO 21 and GPIO 22 are used by default.

Since these pin assignments are preset in underlying driver libraries, beginners do not need to write complex low-level register configuration code.

On the back of the module, two pads or a jumper resistor labeled "Address Select" can often be seen, acting as a physical switch to adjust the wiring logic.

In some highly integrated PCB projects, this 4-wire interface can even be changed to an FPC connector, transmitting via 0.5 mm pitch flexible cables to further compress the space occupied by wiring to the extreme.

When an OLED is fully lit, the current can surge from a few milliamps to over 20 mA.

If the VCC and GND wires among the four I2C cables are too thin or have high contact resistance, the resulting voltage drop can cause noise on signal lines, leading to random snow-like spots or black screens.

Therefore, under the principle of minimal wiring, it is recommended to use slightly thicker wires for the power lines and place a 0.1uF or 10uF decoupling capacitor in parallel near the OLED module's VCC and GND pins.

Such subtle wiring optimizations ensure communication stability in 400kHz fast mode while using only two signal lines.

SPI Resource Occupancy

Compared to the I2C solution, SPI's physical port occupancy increases by 150%.

Although it supports high-speed clocks above 10MHz, every display device added in parallel requires an additional independent CS chip select pin.

This multi-wire parallel mode leads to increased PCB routing area and significantly compresses the remaining IO space for sensors or wireless modules when microcontroller resources are limited.

Standard 4-wire SPI mode usually requires connecting five active signal lines: SCK (Serial Clock), MOSI (Master Out Slave In), CS (Chip Select), DC (Data/Command Select), and RES (Reset).

The SCK clock line synchronizes the pace of the entire data transmission. On high-performance controllers like ESP32 or STM32, the toggle frequency of this pin is typically configured between 10MHz and 20MHz.

This pin not only occupies a GPIO port but also requires high-speed driving capability from the controller, and its physical trace must be as short as possible to avoid impedance mismatch in long wires at high frequencies.

The MOSI pin is responsible for delivering the 128x64 pixel dot matrix binary data bit by bit. At a 60-frame refresh rate, this pin must handle over 490,000 bit switching actions every second.

In a 4-wire SPI physical link, the DC pin is a representative hardware overhead. Unlike the I2C protocol, which inserts control bytes into the data stream, SPI chooses to perform this task via a dedicated physical level.

While SCK, MOSI, DC, and RES can be shared among multiple SPI screens, every display module added to the bus must be assigned a unique CS chip select pin.

If a monitoring system needs to drive three OLED screens simultaneously, physical pin consumption quickly climbs to 7 (4 shared lines plus 3 independent CS lines).

This physical-level mandatory isolation ensures extremely fast communication response but results in a maze of traces in PCB design.

When hand-soldering or using breadboards for prototyping, the arrangement of 5 to 7 signal lines significantly increases the probability of failure due to poor contact.

| Resource Dimension | 4-Wire SPI Occupancy Details | Performance/Physical Impact Data |

|---|---|---|

| GPIO Total | 5 independent ports (single screen) | 150% higher occupancy than I2C |

| Typical Clock Frequency | 10MHz - 20MHz | Data throughput ~25 to 50 times that of I2C |

| Memory Buffer | 1024 bytes (128x64) | Must allocate full-frame mapping space in RAM |

| Device Expansion Cost | +1 GPIO per screen | Bus devices limited by controller pin count |

| Logic Level Demand | 3.3V CMOS | Requires high-quality power decoupling at high frequencies |

| Refresh Latency | ~1-2 milliseconds (full screen) | Extremely low processor blockage, suitable for dynamic UI |

Although the SPI protocol appears simple, developers usually use hardware SPI peripherals (Hardware SPI) rather than software simulation (Bit-Banging) to extract its speed advantages.

Using hardware SPI forces the controller to lock specific functional pins, depriving them of use as general IO or other peripherals (like UART or PWM).

In terms of memory occupancy, to maintain high-speed non-blocking SPI transmission, driver libraries typically need to allocate a RAM buffer exactly matching the screen resolution.

For a 128x64 pixel monochrome OLED, this means 1024 bytes of static memory are permanently assigned.

If powerful graphical libraries like Adafruit GFX or U8g2 are used to achieve smooth scrolling and font rendering, additional Flash storage consumption is usually between 10KB and 30KB, which is an extremely heavy burden for low-end microcontrollers with only 32KB of Flash.

When five signal lines work at 20MHz, their rise times are typically on the order of several nanoseconds.

To prevent signal reflection, traces must maintain continuous impedance, and a constant coupling should be maintained between signal lines and the ground plane.

In contrast, I2C only handles two slow-speed signal lines. SPI resource occupancy is reflected not only in pin count but also in the passive components required to support these pins.

To suppress overshoot in high-speed signals, it is usually necessary to connect 22-ohm to 47-ohm matching resistors in series on the SCK and MOSI lines.

In multi-layer PCB design, SPI signal bundles often require a full routing layer and a large number of vias for layer transitions.

Multi-screen Parallel Connection Differences

In multi-display systems, the I2C protocol uses 7-bit slave addresses to achieve logic addressing.

Multiple screens share the same SDA and SCL signal lines, keeping the total pin count at 2, but the accumulation of bus capacitance limits the number of parallel devices and transmission distance.

The SPI protocol uses CS chip select physical isolation.

Although SCK, MOSI, and DC lines can be reused, every additional screen must occupy an independent GPIO as a chip select signal, with pin overhead increasing linearly with the number of devices.

The I2C solution offers extremely high pin efficiency in dual-screen applications, while the SPI solution provides stronger data throughput independence in multi-screen high-frequency refresh tasks.

For common SSD1306 screens, the protocol supports a 7-bit address space, but due to physical configuration pins led out by the driver chip, developers can typically only configure two different hardware addresses on the same bus, 0x3C and 0x3D.

In practice, one simply connects the first screen's address pin to ground and the second's to high level; these two screens can then be paralleled on the same set of SDA and SCL pins of the microcontroller.

From a PCB layout perspective, this topology allows signal lines to follow a "daisy-chain" scheme from one screen to the next, greatly simplifying routing, especially in 8-bit or 16-bit microcontroller projects where GPIO resources are scarce.

However, this convenience brings electrical challenges. Every OLED module and its connecting wires added increases the bus's equivalent distributed capacitance, typically around 10pF to 15pF per 0.96-inch module.

When total capacitance exceeds the 400pF maximum defined by the I2C standard, signal rising edges become rounded due to long charging times, leading to high-level detection failures.

To mitigate this in multi-screen setups, developers usually need to adjust the pull-up resistors on the bus from 10k ohms down to 2.2k ohms or less to force faster level transitions.

-

Technical Details of I2C Multi-screen Paralleling:

- Pin Consumption: Always only 2 GPIO ports, whether 1 or 2 screens are attached.

- Address Limit: Usually limited to 2 screens for the same model without using I2C multiplexers (like TCA9548A).

- Bandwidth Allocation: All screens share the 400kHz total bandwidth. If two screens refresh full-screen simultaneously, the effective frame rate for each will drop by more than 50%.

- Electrical Matching: As the number of parallel devices increases, pull-up resistance must be precisely calculated and adjusted to offset the timing impact of parasitic cable capacitance.

- Fault Tolerance: Since all screens are on the same bus, a hardware failure in any one screen (e.g., SDA shorting to ground) will paralyze the entire display system or the whole I2C bus.

In a multi-screen environment, the microcontroller's hardware SPI controller leads out a shared signal bundle including SCK (Clock), MOSI (Master-Out), and DC (Data/Command).

All OLED screens are paralleled on these three lines, but each screen's CS pin must connect to an independent GPIO on the microcontroller.

When screen A's image needs updating, the controller pulls CS_A low; meanwhile, CS pins for screens B and C remain high, causing their internal shift registers to enter a high-impedance state and completely ignore data flow on the bus.

This physical isolation ensures signal purity, resulting in extremely low interference between devices even at ultra-high frequencies of 10MHz or 20MHz.

However, the pin consumption formula for this scheme is N+4 (where N is the number of screens, and 4 represents the shared SCK, MOSI, DC, and RES lines).

If a system needs to drive 4 screens, the display section alone will consume 8 GPIO pins, which might crowd out resources for UART communication or sensor acquisition on microcontrollers with only around 20 total pins.

-

Technical Details of SPI Multi-screen Paralleling:

- Pin Growth: 1 screen needs 5 pins, 2 screens need 6 pins, 3 screens need 7 pins (assuming RES is shared).

- Independent Bandwidth: Each screen can exclusively occupy over 10MHz of bandwidth when selected; there is no bandwidth splitting as seen with I2C.

- Chip Select Logic: The CS pin must remain at a stable high level when not selected; any level jitter will cause the screen to erroneously receive garbage data.

- Reset Strategy: In multi-screen setups, the RES reset pin can usually be shared to save IO. However, during system initialization, all screens will reset simultaneously, preventing independent hardware reboots of a single screen.

- Physical Span: Since SPI uses high-frequency single-ended signals, length deviations between branches in multi-screen setups should be kept within 5 cm to avoid phase deviations in the sync clock due to propagation delays.

In I2C mode, driver libraries (like U8g2 or Adafruit_SSD1306) must dynamically change the 7-bit address of the target device in the protocol header before every transmission.

Since every address transmission requires waiting for a slave response (ACK bit), this protocol-level handshake overhead accumulates into noticeable latency during frequent switching between multiple screens.

In SPI mode, software logic manifests as simple level flipping of specific pins.

Before sending a data packet, the processor directly manipulates GPIO registers to pull the corresponding CS low. This process typically takes only 1 to 2 instruction cycles, incurring almost no protocol burden.

This rapid switching capability makes the SPI solution irreplaceable in scenarios requiring synchronized high-dynamic animations across multiple screens.

A single 0.96-inch OLED consumes approximately 20mA to 25mA when fully lit.

When three or four screens are paralleled via I2C or SPI, instantaneous peak current can break 100mA.

Because the parallel structure causes all current to flow toward the same set of VCC and GND pins, if wire diameters are too thin or connector contact resistance is too high, the resulting voltage drop will feed back into the signal lines.

In protocols like I2C, which have strict requirements for level thresholds, power fluctuations often cause false start signals on the SDA line, leading to garbled screen content.

Therefore, for physical wiring, a star-power topology is recommended—where power lines are led independently from the main power source to each screen—while signal lines follow a bus or physical distribution structure based on the protocol's characteristics.

더 읽기

TFT LCD has deeply established itself in the industrial display field with high-brightness backlighting exceeding 1000 nits and excellent cost-durability. Meanwhile, self-emissive OLED has set a ne...

AMOLED relies on a TFT active matrix to achieve an ultra-fast response time of less than 1ms, making it the preferred choice for high-definition large screens; PMOLED features a simple structure an...

댓글 남기기

이 사이트는 hCaptcha에 의해 보호되며, hCaptcha의 개인 정보 보호 정책 과 서비스 약관 이 적용됩니다.