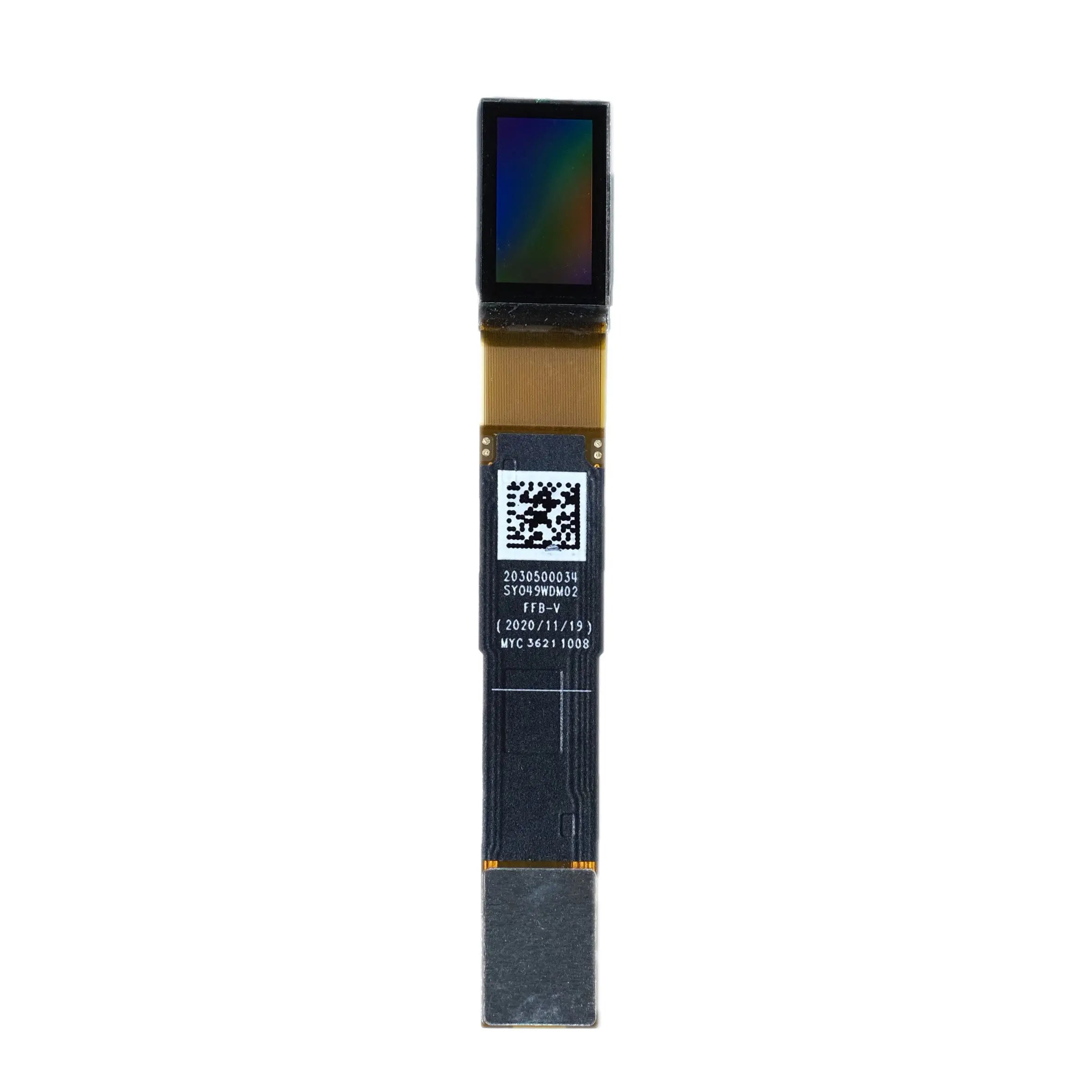

The COG process utilizes Anisotropic Conductive Film (ACF) under thermal compression at approximately 200°C to directly bond the driver IC to the glass substrate.

It achieves vertical conduction by crushing 3-micron conductive particles within the film, eliminating the need for a PCB and significantly reducing the module volume.

Structure

Unlike conventional packaging, the I/O pads of a COG driver IC are grown with Gold Bumps approximately 9-15µm high. Physical fixation between the two is achieved through an Anisotropic Conductive Film (ACF) that is only 20-50µm thick.

The ACF contains polymer conductive spheres with a density of about 3000-5000 pcs/mm². Under the pressure applied by the thermal head, these microspheres, 3-5µm in diameter, rupture and deform, establishing current conduction in the vertical direction (Z-axis) while controlling contact resistance to within 5 Ohms.

Glass Ledge Design

In standard 5.5-inch to 6.7-inch mobile device display modules, the TFT substrate is typically 3.5 mm to 6.0 mm longer than the upper Color Filter (CF) substrate.

This area is not a simple glass surface but a complex functional zone integrated with high-density metal leads, test circuits, alignment marks (Fiducial Marks), and electrostatic discharge (ESD) protection rings.

To adapt to the market demand for Narrow Bezels, modern processes control glass cutting precision to within ±0.03 mm.

Simultaneously, to ensure mechanical rigidity during the Bonding process, the backlight module's iron frame beneath this area is usually designed with a dedicated support structure to prevent the glass from chipping or deforming under the thermal head pressure of 50 to 100 MPa.

At the electrical connection level, the trace layout on the Ledge area directly determines the integrity of the display signal.

Although transparent Indium Tin Oxide (ITO) must be used in the pixel area, in the Ledge area, low-impedance metal stack structures such as MAM or Titanium-Aluminum-Titanium are typically used to cover the ITO to reduce line impedance.

The sheet resistance of pure ITO is typically 30 to 50 Ohms/square, which is too high for Gate signals driven at voltages as high as 20V or more, leading to signal delay (RC Delay) and waveform distortion.

By introducing a metal layer, the sheet resistance of the lines can be reduced to below 0.2 Ohms/square.

On the output side of the driver IC, due to the extremely high number of pins, the routing must adopt a Fan-out design.

To ensure signals on all data channels arrive synchronously, the routing in the Fan-out area requires an equal resistance design.

This involves adjusting line widths or artificially increasing the length of serpentine traces so that the shortest path in the middle and the longest path at the edges have the same resistance value.

Typically, the resistance deviation between channels is required to be controlled within 1% to 3% to prevent vertical unevenness stripes in the image.

| Trace Area | Typical L/S (Line/Space) | Material Composition | Impedance Requirement | Function Description |

|---|---|---|---|---|

| IC Input Side | 30µm / 30µm | Metal + ITO | < 5 Ω | Carries MIPI/LVDS high-speed signals and power input; requires low impedance to prevent interference. |

| IC Output Side | 10µm / 10µm | ITO (Partially Metal Coated) | 500 ~ 2k Ω | Connects IC to the pixel area; extremely high density; impedance balanced via Fan-out. |

| FPC Binding Area | 150µm / 150µm | Metal + ITO | < 1 Ω | Wide contact pads used for ACF compression with FPC gold fingers. |

The Pad Layout of the driver IC on the glass usually adopts a multi-row Staggered design to solve the problem of excessively small pin pitch.

As screen resolutions rise to over 400 PPI, the pin pitch for a single linear arrangement would have to shrink to below 10 microns.

This would exceed the process limit of ACF conductive particles (diameter 3-5 microns), easily causing lateral short circuits.

Therefore, pad design on the Ledge often employs two or even three staggered rows, expanding the Effective Pitch to 15 to 25 microns.

This design requires the photolithography process on the glass substrate to possess extremely high alignment precision.

At the corners of the Ledge, specialized Optical Alignment Marks are usually etched.

These marks are typically cross-shaped or concentric circles made of high-contrast Chromium (Cr) for recognition by the automatic bonding machine's CCD camera system.

The machine vision system captures the marks on the glass and the corresponding marks on the driver IC.

By fine-tuning the platform position, it ensures the IC's gold bumps land accurately on the center of the glass pads.

The allowable X/Y axis offset is usually strictly limited to within 3 microns.

Furthermore, the Ledge area is a key location for production testing. Before FPC bonding, panel factories usually utilize test pads (Shorting Bars) reserved at the edge of the Ledge to perform Cell Tests (lighting tests).

After detection is complete, these test circuits are usually physically cut via laser cutting or dicing processes, or specific circuit designs are used to keep them in a high-impedance state during module operation.

Regarding environmental durability, the cutting quality of the glass ledge edge is crucial.

Micro-cracks left by mechanical wheel cutting can become channels for moisture intrusion in high-temperature and high-humidity environments, leading to corrosion and open circuits in the ITO lines.

Chip Bumping Process

The entire manufacturing flow begins with a whole 8-inch or 12-inch wafer. First, Physical Vapor Deposition (PVD) or sputtering processes are used to cover the original aluminum pads and passivation layer surface with a layer of Under Bump Metallurgy (UBM) metal.

The UBM layer typically consists of two parts: the bottom layer is Titanium Tungsten alloy (TiW) or Titanium (Ti) with a thickness of about 1000 to 3000 Angstroms (Å), acting as an adhesion layer and a diffusion barrier to prevent gold atoms from migrating into the silicon circuits below;

The upper layer is Gold (Au) or Palladium (Pd) with a thickness of about 500 to 1000 Angstroms, serving as a Seed Layer to provide a conductive base for the subsequent electroplating process.

Since the pin density of COG driver chips is extremely high, the etching precision of the UBM directly affects the root size of the bumps.

Lateral Undercut must be controlled within 0.5 microns to maintain the mechanical strength of the bump base.

Photolithography defines the geometric shape and positional accuracy of the gold bumps.

Unlike traditional logic chip manufacturing, the bumping process requires the use of high-viscosity Thick Photoresist.

Spin coating thickness is usually between 20 to 30 microns to accommodate the final bump height requirement of 15 to 18 microns.

After high-energy exposure and development by a Stepper, an array of deep holes with extremely high verticality is formed on the wafer surface.

Subsequently, the wafer is immersed in an electrolyte tank containing sodium gold sulfite or potassium gold cyanide for electroplating.

To obtain a dense gold grain structure, current density is strictly controlled within the range of 0.3 to 0.8 A/dm², and the electrolyte temperature is maintained at 40 to 60 degrees Celsius, accompanied by strong mechanical stirring to eliminate ion concentration differences in the diffusion layer.

The gold layer grows upwards within the cavity defined by the photoresist at a speed of 0.2 to 0.5 microns/minute until it reaches the preset height.

Due to uneven current distribution, bump height differences between the edge and center of the wafer are inevitable.

Electroplating equipment controls the bump height range (Within Wafer) to within 1.0 micron through the adjustment of anode Shielding Plates.

After removing the photoresist and etching away the excess UBM layer, the exposed gold bumps need to undergo high-temperature Annealing.

This step is usually performed in a nitrogen environment at 250 to 350 degrees Celsius for 30 to 60 minutes.

The purpose is to release internal stresses accumulated during the electroplating process and cause recrystallization of the gold grains.

The hardness of the gold bumps after annealing will drop from over 100 Hv in the as-plated state to 40 to 75 Hv.

This hardness range is precisely calculated: the bumps must be harder than the conductive particles in the ACF (usually polymer spheres with nickel-gold plating) to ensure they can pierce the insulating film on the particle surface;

Simultaneously, they must be softer than the ITO lines on the glass substrate to prevent crushing the glass or causing ITO fracture under the bonding pressure of 80 MPa.

To match ACFs of different densities, the bump surface must possess extremely high flatness. Surface roughness (Ra) is typically required to be lower than 0.2 microns.

Any protruding Nodules could lead to excessive local pressure during bonding, puncturing the anisotropic conductive film and causing short circuits.

The quality inspection link mainly relies on fully Automatic Optical Inspection (AOI) and laser profilometers.

For Fine Pitch COG driver chips, the Coplanarity of the bumps is the top priority for inspection.

The height difference between the highest and lowest points of all bumps on a single chip must be less than 2 microns; otherwise, some pins will fail to contact the conductive particles, causing Open circuit failures.

In addition, the Shear Test is used to verify the bonding force between the bump and the aluminum pad.

Standards require that a bump with a diameter or side length of 30 microns can withstand a lateral thrust of at least 30 grams force without peeling.

Conductive Glue Layer Composition

Anisotropic Conductive Film (ACF) in COG packaging is not a single chemical agent but a complex composite material system composed of a thermosetting resin matrix and high-precision conductive microspheres. It is usually supplied in tape form, structurally containing a PET release film (thickness 38 to 50 microns), an adhesive layer (thickness 10 to 35 microns), and a protective film.

Its physical form is designed to be in a semi-solid B-Stage state at room temperature. Once subjected to the high temperature of 180 to 220 degrees Celsius applied by the Bonding machine's thermal head, the latent curing agent within the resin system activates rapidly within 1 to 2 seconds.

The viscosity drops instantly to fill the micron-level gap between the chip and the glass, followed by 85% to 95% cross-linking curing reaction within 5 seconds, forming a rigid polymer network with extremely high modulus that permanently locks the driver IC's gold bumps to the ITO line surface of the glass substrate.

The electrical performance of ACF relies entirely on the Conductive Particles dispersed within it. For modern COG processes with pin pitches smaller than 20 microns, the diameter of these particles is strictly screened to be between 2.8 and 4.0 microns, and the standard deviation (CV value) of the particle size distribution must be controlled within 5%.

Unlike solder balls used in PCB soldering, conductive particles for COG use a "Polymer Core + Metal Plating" structure:

- Polymer Core: Usually made of cross-linked polystyrene (DVB) or acrylic resin, possessing a precisely tuned elastic modulus (K-Value). It can undergo 30% to 50% deformation during the compression process without breaking, using the material's rebound force to maintain physical contact with the electrodes.

- Metal Plating: The core surface is first electrolessly plated with a layer of Nickel (Ni) about 0.1 microns thick as a barrier layer and hardness support, followed by a layer of 0.05 microns of Gold (Au) to reduce contact resistance and prevent oxidation.

- Insulation Coating: This is a special design for high-density COG. To prevent lateral high-density conductive particles from clustering and short-circuiting, the outermost layer of each microsphere absorbs a layer of insulating resin particles or insulating film only 50 to 100 nanometers thick.

To adapt to the ultra-fine pin pitch (Fine Pitch) required by 4K or even 8K panels, the particle density in ACF must reach extremely high levels, typically containing 4000 to 20000 conductive particles per square millimeter.

This high-density distribution aims to satisfy the statistical "Particle Capture Rate," ensuring that every tiny gold bump (area may be only 600 square microns) "captures" at least 5 to 10 effective conductive particles underneath.

If the number of captured particles is insufficient, contact resistance becomes unstable; if the quantity is excessive and unevenly distributed, it may lead to particle stacking, causing bump deformation or excessive stress on the glass substrate leading to cracking.

The epoxy resin matrix acts as the continuous phase of the ACF. It not only carries the conductive particles but also determines the mechanical reliability and weather resistance of the module.

The resin formula typically contains Bisphenol A type or modified epoxy resins, imidazole or cationic curing agents, and silane coupling agents.

- Glass Transition Temperature (Tg): The Tg point of the cured resin is usually set at 120 to 150 degrees Celsius, higher than the normal operating temperature of the device, to ensure the colloid does not soften and cause particle rebound failure when heated.

- Coefficient of Thermal Expansion (CTE): The CTE of the resin needs to be adjusted to 40 to 60 ppm/degree Celsius (in the Alpha 1 stage), aimed at alleviating shear stress generated by the thermal expansion and contraction difference between the silicon chip (CTE ~3 ppm) and the glass substrate (CTE ~4-8 ppm).

- Rheology: In the initial stage of thermal compression, the minimum melt viscosity of the resin is typically controlled at 2000 to 5000 mPa·s to ensure the glue can smoothly expel air bubbles from the bottom of the chip and fill the voids around the bumps, preventing Voids. Any residual bubbles could expand and burst or accumulate moisture leading to electrochemical migration during subsequent high-temperature high-humidity testing.

Once bonding is complete, the cured resin layer not only provides a Peel Strength of 8 to 12 Newtons/cm but also seals the conductive particles in an airtight environment.

At this point, the flattened conductive particles act like miniature springs. Assisted by the contraction force of the resin, they continuously apply reverse pressure to the upper and lower electrodes, thereby maintaining a low-resistance connection throughout the full lifecycle.

For high-frequency applications, the Dielectric Constant (Dk) and Dielectric Loss (Df) of the resin also need optimization to reduce transmission loss for high-speed signals (such as MIPI C-PHY 2.5Gsps).

Signal Transmission Flow

The complete signal link begins with high-speed differential signals output by the mobile processor Application Unit (AP), typically following MIPI D-PHY or C-PHY protocol standards, transmitting at a rate of 1.0 to 2.5 Gbps per channel.

These low-swing (usually 0.2V to 0.4V) high-frequency signals first traverse the multi-layer copper foil circuits of the Flexible Printed Circuit (FPC) board to reach the FPC-to-glass substrate bonding interface (OLB).

Here, the current must penetrate the ACF conductive layer on the FPC side and enter the metal traces in the glass substrate Ledge area.

Since the input traces on the glass substrate bear the burden of data transport, to control transmission loss within -3dB and prevent signal Eye Diagram closure, this part of the traces does not use high-impedance transparent ITO but is composed entirely of low-resistivity metal stacks like Aluminum/Molybdenum/Titanium.

The trace impedance is strictly limited within the characteristic impedance range of 50 to 100 Ohms, and Ground (GND) shield lines are inserted between adjacent differential pairs to reduce Crosstalk to below -20dB.

Signal integrity engineers typically define the input path on the glass substrate as a "lossy transmission line model." This means that as frequency increases, signal amplitude decays exponentially due to the skin effect and dielectric loss; therefore, this physical path length is usually restricted to within 5 mm.

The process of entering the driver IC occurs at the gold bump contact points on the Input Side.

Signal current flows vertically through the gold-plated polymer spheres in the ACF into the interface circuits inside the chip.

Inside the chip, logic control signals (1.2V/1.8V) are processed by Level Shifters and Digital-to-Analog Converters (DACs) and converted into analog voltages that can directly drive the deflection of liquid crystal molecules.

This conversion process involves extremely complex voltage domain crossing:

- Logic Voltage (Logic V): 1.2V ~ 1.8V, used for processing image data and timing control.

- Source Driver Voltage (Source V): +/- 5.0V ~ 6.0V, determines the grayscale brightness of each sub-pixel.

- Gate Turn-On Voltage (VGH): 18V ~ 25V, used to turn on TFT switches and charge capacitors.

- Gate Turn-Off Voltage (VGL): -6V ~ -10V, used to turn off TFTs and maintain pixel charge.

For an FHD+ screen with a resolution of 2400 x 1080, the driver IC needs to simultaneously output 3240 Source drive signals (1080 x 3 RGB) outwards through the gold bumps on the Output Side.

After these currents flow out of the chip, they immediately enter the Fan-out sector trace area on the glass substrate.

This is a physical bottleneck area because over 3000 lines must rapidly spread out from the dense arrangement of chip pins (Pitch < 20µm) to connect to the pixel array in the display area within a vertical distance of only 3 to 4 mm.

To ensure the central 1620th channel has the same signal delay as the outermost 1st channel, wiring design must strictly enforce "Equal Resistance Constraints."

Designers will artificially add Serpentine Traces or reduce line widths on low-impedance channels, forcing the Total Trace Resistance of all output channels to stabilize uniformly between 3000 and 5000 Ohms, with impedance differences between channels locked within an extremely narrow tolerance of ±2%.

Bonding Process

The COG bonding process utilizes ACF (Anisotropic Conductive Film) as a connection medium, using Thermal Compression technology to fix the driver IC's gold bumps to the ITO trace area of the glass substrate.

This process requires the head temperature to be precisely controlled between 190°C and 230°C, applying a pressure of 60 to 100 MPa for 3 to 5 seconds.

This operation causes the polymer conductive spheres with a diameter of about 3 to 5 microns inside the ACF to undergo 20% to 50% physical deformation, thereby establishing a low-resistance channel in the vertical Z-axis direction, while using the cured epoxy resin to maintain insulation in the horizontal X/Y axis directions, preventing short circuits between pins with spacing less than 20 microns.

ACF Material Composition

The basic physical form of ACF consists of Insulating Adhesive, which typically makes up 85% to 95% of the volume.

In COG applications, due to the need for high-temperature and high-humidity reliability, the industry universally adopts Epoxy Resin systems rather than Acrylic systems used for low-end connections.

The epoxy resin formula contains base resin, Curing Agent, and silica filler used to adjust the Coefficient of Thermal Expansion (CTE).

Modern ACF widely uses Latent Curing Agent technology.

When the thermal head conducts temperature to the ACF layer and exceeds the critical point (usually 80°C to 120°C), the microcapsule shell ruptures or melts, releasing active substances to trigger a rapid cross-linking reaction.

This chemical reaction needs to complete more than 90% of the degree of cure within 3 to 5 seconds, rapidly transforming the resin from a viscous flow state to a high-modulus glassy state, thereby maintaining the compressed state of the conductive particles via mechanical locking force after external pressure is removed.

The Glass Transition Temperature (Tg) of the cured resin is usually designed between 100°C and 130°C to ensure the material remains rigid within the device's operating temperature range, preventing Z-axis rebound and contact failure due to thermal expansion.

Conductive Particle Architecture

Conductive Particles dispersed in the resin matrix are the carriers for achieving electrical connection.

Their diameter in COG processes is typically strictly controlled between 3 microns and 4 microns, with a particle size distribution standard deviation of less than 0.1 microns.

Unlike solid metal balls or carbon spheres used in the early days, modern COG-specific ACFs almost exclusively use Metal-Plated Polymer Spheres.

This composite structure contains three main functional layers: The innermost layer is a Cross-linked Polystyrene or acrylic polymer core, possessing a precisely tuned elastic modulus (K-value) to store mechanical energy like a spring after compression;

The middle layer is a Nickel (Ni) plating, about 0.05 microns to 0.1 microns thick, providing hardness and a corrosion barrier;

The outermost layer is a Gold (Au) plating, about 0.05 microns thick, used to provide low contact resistance and prevent oxidation.

Insulation Coating Technology

As display panel resolutions increase, the pin Pitch of driver ICs has shrunk to 15 microns or even lower, drastically increasing the risk of short circuits between adjacent pins.

To solve this, high-density ACF adopts Insulation Coated Conductive Particle technology.

Manufacturers adsorb a layer of nano-scale insulating resin powder or form an extremely thin insulating film on the outermost periphery of the gold plating, with a thickness usually between 10 nanometers and 50 nanometers.

Physically, these particles are insulated on the surface when uncompressed. Therefore, even if particles aggregate and touch each other at high density in the X/Y plane, no lateral current is generated.

Only when subjected to a vertical pressure of over 60 MPa in the Z-axis direction is this nano-insulation layer mechanically pierced by the upper and lower electrodes, exposing the internal gold conductive layer to achieve conduction.

This design allows particle density in ACF to increase from the conventional 3,000 particles/mm² to over 20,000 particles/mm², while maintaining extremely high insulation resistance.

The table below lists the material layering parameters of common conductive particles in COG ACF:

| Layer Structure | Material Composition | Typical Thickness | Physical Function |

|---|---|---|---|

| Core | Cross-linked Polystyrene (PS) | 3.0 µm - 4.0 µm | Provides rebound force, compensates for thermal expansion difference |

| Barrier | Nickel | 50 nm - 100 nm | Increases structural rigidity, prevents metal diffusion |

| Conductor | Gold | 40 nm - 60 nm | Lowers contact resistance, oxidation resistance |

| Insulation | Thermoplastic Resin Powder | 10 nm - 50 nm | Prevents X/Y axis lateral short circuits, ruptures under pressure for conduction |

Fillers and Additives

Silane Coupling Agents are used to modify the interfacial bonding force between inorganic glass surfaces and organic resins, specifically to prevent interface peeling caused by moisture infiltration in high-humidity environments.

To match the thermal expansion characteristics of silicon chips (CTE approx. 3 ppm/°C) and glass substrates (CTE approx. 3-9 ppm/°C), micron or nano-scale Silica particles are added to the formula as inert fillers.

These fillers do not participate in chemical reactions but can effectively reduce the overall thermal expansion coefficient of the resin matrix (typically reducing pure resin from 60-80 ppm/°C to 30-40 ppm/°C), minimizing residual internal stress during the cooling process.

Additionally, to control rheological properties, leveling agents and thixotropic agents are added to ensure the ACF has good initial Tackiness during lamination, while being able to rapidly fill pin gaps and expel bubbles during the thermal compression flow stage.

Process Flow

In the initial stage of the COG bonding process, the glass substrate must undergo rigorous surface treatment to meet the cleanliness requirements of micron-level connections.

After being transported to the cleaning station, the substrate first has macroscopic particles removed via high-pressure deionized water spray or organic solvent ultrasonic cleaning.

Subsequently, it enters an atmospheric Plasma cleaning unit or UV Ozone cleaning unit.

This step utilizes oxygen free radicals to bombard the ITO (Indium Tin Oxide) conductive layer surface, decomposing attached organic hydrocarbons into carbon dioxide and water vapor.

Simultaneously, it reduces the contact angle of the ITO surface from the usual 40 to 60 degrees to below 10 degrees.

This significant increase in surface energy increases the Dyne value, ensuring the subsequent ACF resin can fully wet the glass surface, avoiding microscopic voids or bubbles caused by interfacial tension differences, as these microscopic defects are often the starting points for circuit corrosion in high-temperature high-humidity environments.

The cleaned substrate immediately enters the ACF lamination station. ACF tape is supplied in reels, with feed length precisely controlled by servo motors.

The Laminator Head pre-laminates the ACF onto the pin area of the glass substrate at a temperature of 60°C to 80°C and a low pressure of 1 MPa to 2 MPa, typically for only 1 to 2 seconds.

This stage employs a Half-cut process, where the blade cuts only the ACF adhesive layer without cutting the underlying Release Liner, which is then peeled off by a robotic arm.

During this process, ionizers must be used to continuously eliminate static electricity generated by the film peeling action, preventing static from attracting airborne dust onto the glue surface.

The laminated ACF must cover all ITO pin areas, and the glue overflow at the edges needs to be controlled between 0.2 mm and 0.5 mm to ensure the insulating resin can completely wrap the edges of the subsequently placed IC.

IC pick-and-place and pre-alignment are key steps connecting the adhesive material and the chip.

The Flip Chip is ejected from the wafer tray or Blue Tape by ejector pins and picked up by a nozzle, with the chip's Active Side facing down.

A high-precision visual system uses CCD cameras to simultaneously capture the Fiducial Marks on the glass substrate and the corresponding marks on the IC bump face.

After alignment is complete, the Pre-bonding Head presses the IC onto the ACF at a lower temperature (about 60°C to 100°C) and pressure to fix it initially.

The main purpose of pre-bonding is to prevent the IC from slipping during high-speed transport to the main bonding station.

At this time, the resin in the ACF only softens slightly; polymerization reactions are strictly prohibited, otherwise, the resin will fail to flow and expel bubbles during the main bonding stage.

After entering the Main Bonding station, process parameters reach their peak; this is the decisive moment for physical connection formation.

The Thermode (main bonding head) is usually made of titanium alloy or molybdenum alloy with high thermal conductivity, and its surface is taped with a layer of Teflon or silicone buffer tape 50 microns to 100 microns thick to distribute pressure evenly and protect the back of the IC from crushing.

The head temperature rises rapidly to 190°C to 230°C, and the pressure applied to the back of the IC is calculated based on the total bump area, typically set at 60 MPa to 100 MPa.

During the bonding cycle of 3 to 5 seconds, the ACF undergoes a drastic rheological process: within the first 1 second, high temperature causes resin viscosity to drop instantly to its lowest point, and pressure drives the resin to flow rapidly around the IC and fill the bump gaps;

In the subsequent 2 to 3 seconds, as the latent curing agent activates, the resin undergoes a cross-linking reaction, and viscosity rises sharply until cured.

During this period, the conductive particles captured between the gold bumps and the ITO are vertically compressed.

The particle diameter is compressed to 60% to 70% of its original size, and the gold bumps embed into the metal plating of the particles, forming a metal-to-metal cold weld contact.

Temperature and Pressure Settings

Since the heat from the Thermode must pass through the buffer material and the silicon chip itself to reach the ACF adhesive layer, the Tool Temperature typically needs to be set 20°C to 50°C higher than the curing temperature required by the ACF datasheet.

In actual production, if the ACF requires curing conditions of 180°C / 5 seconds, the head temperature on the equipment side typically needs to be set between 220°C and 240°C.

The efficiency of heat transfer depends on the thickness of the chip. For a standard driver IC with a thickness of 0.5 mm, the heat conduction delay is approximately 0.2 seconds to 0.5 seconds;

For chips thinned to 0.3 mm or thinner, heat conduction speeds up, and the set temperature needs to be reduced accordingly to prevent the ACF adhesive from undergoing premature Skinning before flow filling is complete, which would hinder bubble expulsion.

Process engineers must verify the real-time temperature Profile by embedding K-type thermocouples between the glass substrate and a dummy chip, ensuring that during the 3 to 5 seconds bonding time, the actual temperature of the ACF layer maintains above 180°C and does not exceed 210°C, avoiding high-temperature resin decomposition or generation of micro-voids.

The logic for pressure parameter settings strictly follows "Pressure (Stress) Conservation" rather than simple "Force Conservation." The calculation basis is the total surface area of all Gold Bumps on the driver IC.

The calculation formula for set pressure is: Equipment Output Force (Newton) equals Total Area of all Gold Bumps (square millimeters) multiplied by Target Pressure (MPa).

To ensure ideal deformation of conductive particles with diameters of 3 microns to 4 microns, the target pressure is usually set between 60 MPa and 120 MPa.

If a driver IC contains 1000 input/output pins, and each pin's gold bump size is 15 microns x 100 microns, the effective total area is approximately 1.5 square millimeters.

In this case, if the target pressure is set to 80 MPa, the vertical force applied by the equipment should be 120 Newtons (approx. 12.2 kgf).

It is worth noting that besides functional pins, the four corners of modern driver ICs are usually designed with ineffective "Dummy Bumps." These bumps do not transmit electrical signals but count towards the total compression area.

Their main function is to balance the force on the four corners of the chip, preventing chip warping or slippage due to uneven pressure distribution.

Pressure that is too low leads to particle deformation less than 20% and unstable contact resistance; pressure that is too high, exceeding 150 MPa, may crush the ITO lines under the glass substrate or cause particles to puncture the passivation layer on the gold bump surface.

To achieve uniform pressure distribution between the rigid head and the fragile silicon chip, Buffer Material selection and management are introduced into the process.

- Material Characteristics: Typically Polyimide or Teflon tape is used, with thickness controlled at 50 microns to 100 microns. This material must possess high heat resistance and a certain elastic recovery rate.

- Buffering Mechanism: The buffer tape compensates for the micron-level Planarity unevenness of the head surface and the tolerance of chip thickness. If the height difference between the left and right sides of the head exceeds 2 microns, without buffer tape, it would lead to crushed particles on one side and open circuits on the other.

- Wear and Replacement: Buffer tape undergoes plastic deformation or carbon buildup during repeated high-temperature high-pressure cycles. It is usually set to automatically scroll to change position every 1000 to 2000 bondings to ensure the state of the pressure transmission medium remains consistent.

Since the thermal expansion coefficient (CTE) of silicon chips is about 2.6 ppm/°C, while that of ordinary glass substrates is about 8.5 ppm/°C, at high temperatures of 200°C, the expansion of the glass is far greater than that of the chip.

If pressure is removed directly when the ACF resin is fully cured and the temperature is extremely high, the shear stress generated by the glass retracting will instantly pull on the newly established conductive particle connections.

Therefore, advanced COG equipment adopts a "Pressure-maintaining Cooling" strategy. While the main head maintains 100% of the set pressure, an air cooling system forces the temperature down from 220°C to below 160°C rapidly, allowing the resin to complete phase change and freeze its structure while under pressure.

Read more

Manufacturing requires the use of vacuum thermal evaporation technology to deposit an organic material layer with a total thickness of approximately 150 nanometers on the ITO anode. It achieves pro...

Customization requires first locking down the FPC shape and interface, with a prototyping cycle of about 15 days. During mass production, ACF thermal compression parameters are strictly controlled,...

Leave a comment

This site is protected by hCaptcha and the hCaptcha Privacy Policy and Terms of Service apply.