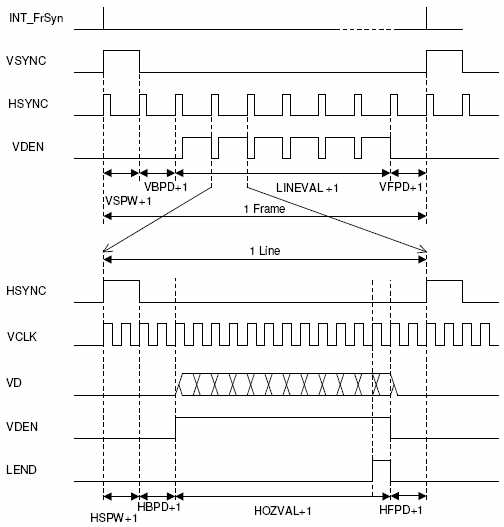

Typical Timing Diagram

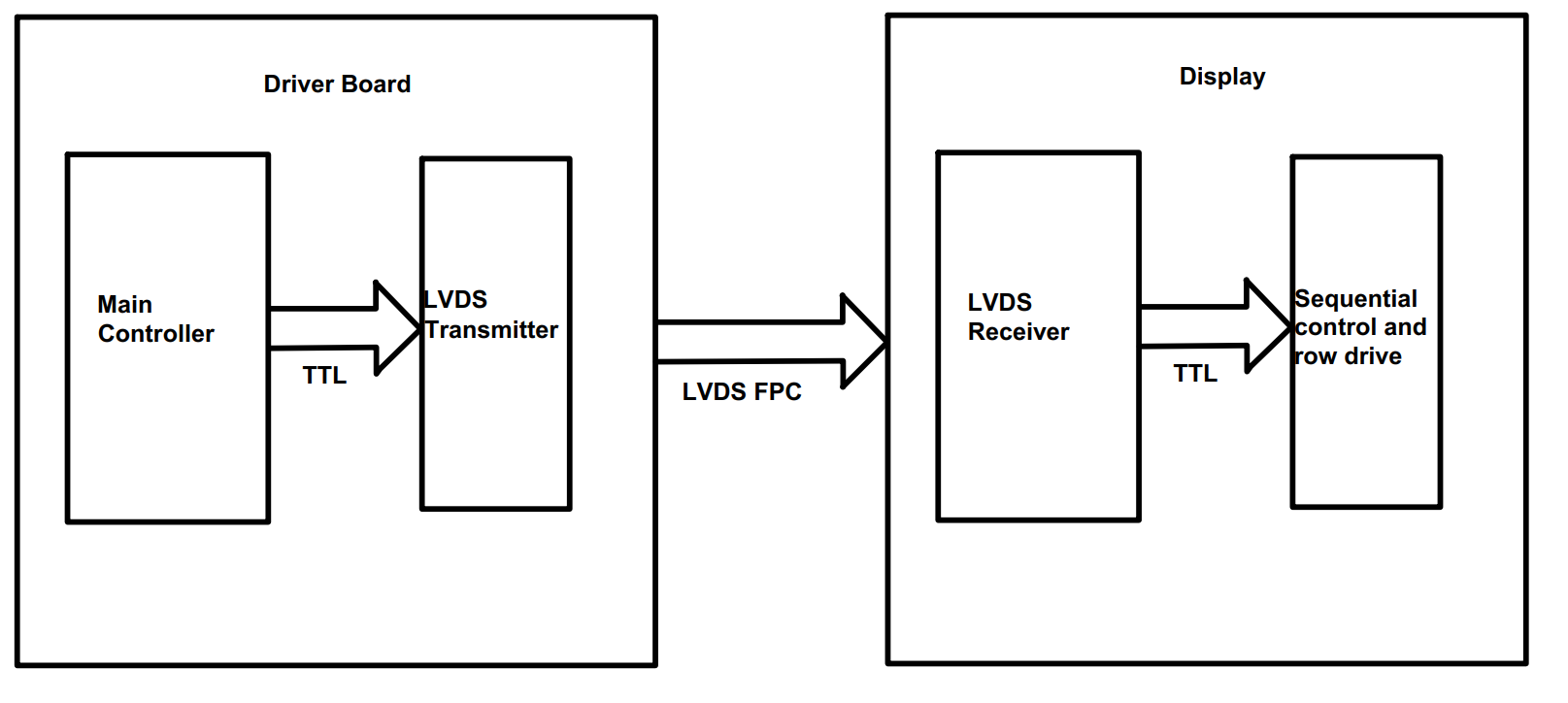

LCD Display Flow

An LCD displays a picture, filling in every pixel, but at a speed that our eyes don't notice. If the LCD display frequency is reduced, we can obviously feel the flickering phenomenon of the whole screen.

We divide LCD screens into horizontal and vertical directions.

Generally, our rows are in the horizontal direction, and the pixels of each LCD row are filled one by one. After filling one row, the next row is filled. The filling order can be left ->. Right or right -> On the left

Each frame is filled from the first pixel in the first row to the last pixel in the last row.

LCD Timing

LCK(Pixel clock)

In the image above, CLK is the pixel clock, sending one pixel of data per clock cycle. According to the parameters of our LCD, for example, there are 800 pixels in a row, then after 800 CLK clocks, we have filled 800 pixels.

HSYNC

HSYNC (Indicates the horizontal synchronization signal), indicating the start of a row of data. The details are as follows:

There is no change in CLK except HSYNC and DEN signals.

The red arrow in the figure indicates that a new line of data transfer starts immediately when HSYNC produces the change shown in the figure. The data transferred during the ENB signal line is considered valid data. In this way, a row of 800 pixels of data can be transferred correctly.

VSYNC

The VSYNC signal in the image below, when the change occurs, indicates that a new frame of data is transmitted immediately.

Fill the new data frame from the first pixel in the first row of the LCD. As mentioned earlier, each row has its own synchronization signal, and each row also has a corresponding data signal line. Therefore, the Vsync signal only cares about the synchronization of one frame (8000*480), and does not care about the synchronization of each line.

Combined with the above several clocks is a typical timing diagram of RGB888.

Read more

Overview LVDS=Low-Voltage Differential Signaling,The core of this technology is the use of very low voltage swing high speed differential transmission data, has the following characteristics: Low ...

An AMOLED screen typically lasts for about 15,000 hours before noticeable dimming occurs, whereas LCDs with LED backlights can exceed 50,000 hours. However, AMOLEDs are prone to permanent burn-in f...

Leave a comment

This site is protected by hCaptcha and the hCaptcha Privacy Policy and Terms of Service apply.